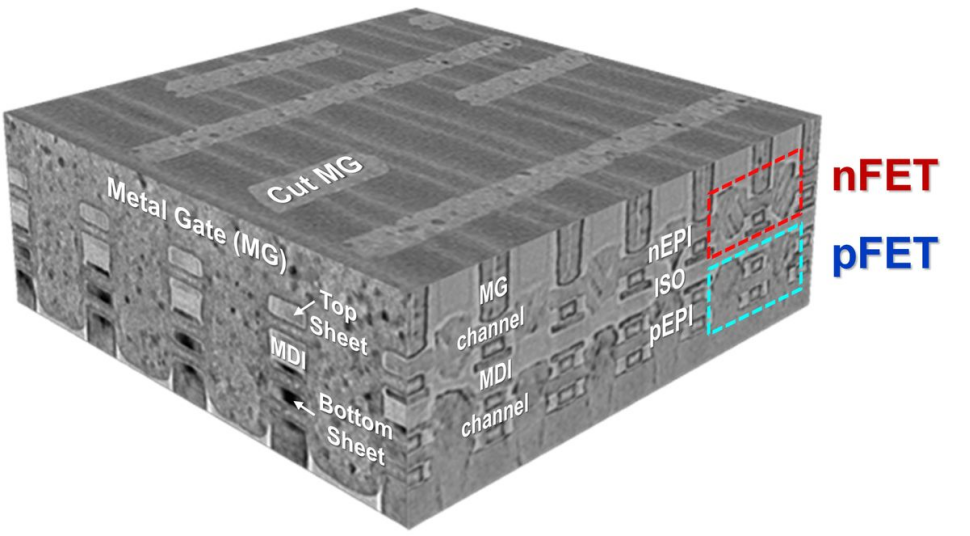

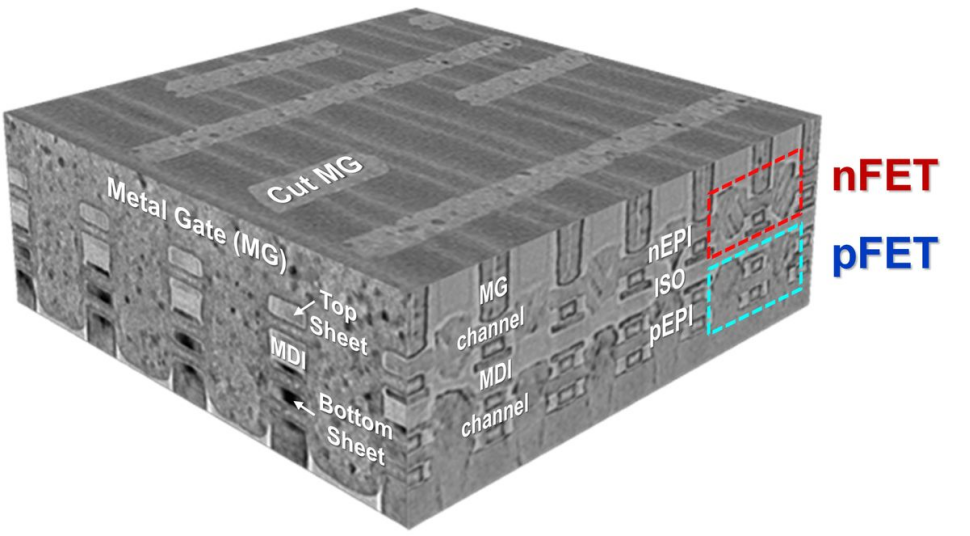

随着三家先进芯片制造商都展示了CFETS(互补场效应晶体管),未来处理器的晶体管密度将增加近一倍的设想已初具雏形。CFET是一种单一结构,堆叠了CMOS逻辑所需的两种类型的晶体管。在本周于旧金山举行的IEEE国际电子设备会议上,英特尔、三星和台积电展示了他们在晶体管领域的新进展。芯片公司正在从2011年开始使用的FinFET器件结构过渡到纳米片或全栅晶体管。这些名称反映了晶体管的基本结构。在FinFET中,栅极控制流过垂直硅鳍的电流。在纳米片器件中,鳍被切割成一组带,每一个都被栅极包围。CFET基本上采用一个更高的色带堆叠,一半用于一个设备,另一半用于另一个设备。正如英特尔工程师在2022年12月的IEEE Spectrum中所解释的那样,该器件在单个集成工艺中构建了两种类型的晶体管nFET和pFET。专家估计 CFET 将于七到十年后投入商业应用,但在准备就绪之前仍有大量工作要做。

英特尔的逆变器

英特尔是三家公司中最早展示CFET的,早在2020年的IEDM上就推出了早期版本。这一次,英特尔报告了围绕CFET制造的最简单电路——逆变器——的几项改进。CMOS反相器将相同的输入电压发送到堆栈中的两个器件的栅极,并产生与输入逻辑相反的输出。英特尔组件研究小组首席工程师 Marko Radosavljevic 在会议前对记者表示:“逆变器是在单个鳍片上完成的。”他说,“在最大缩放比例下,它将是普通 CMOS 逆变器尺寸的 50%”。

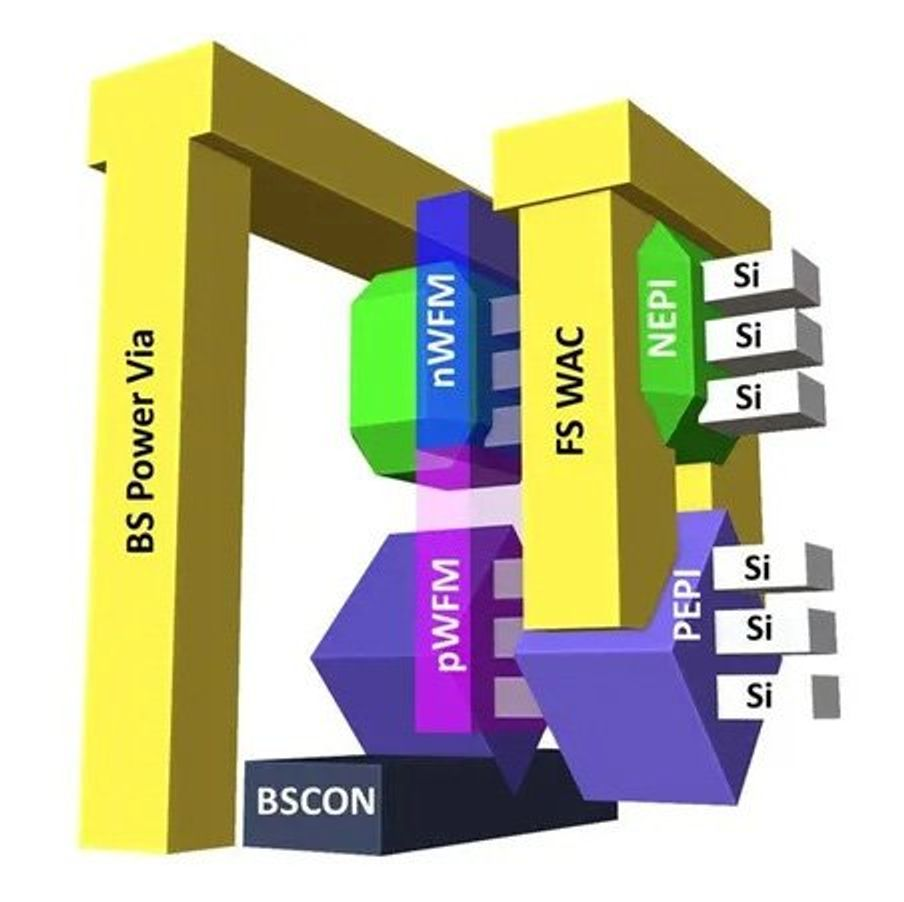

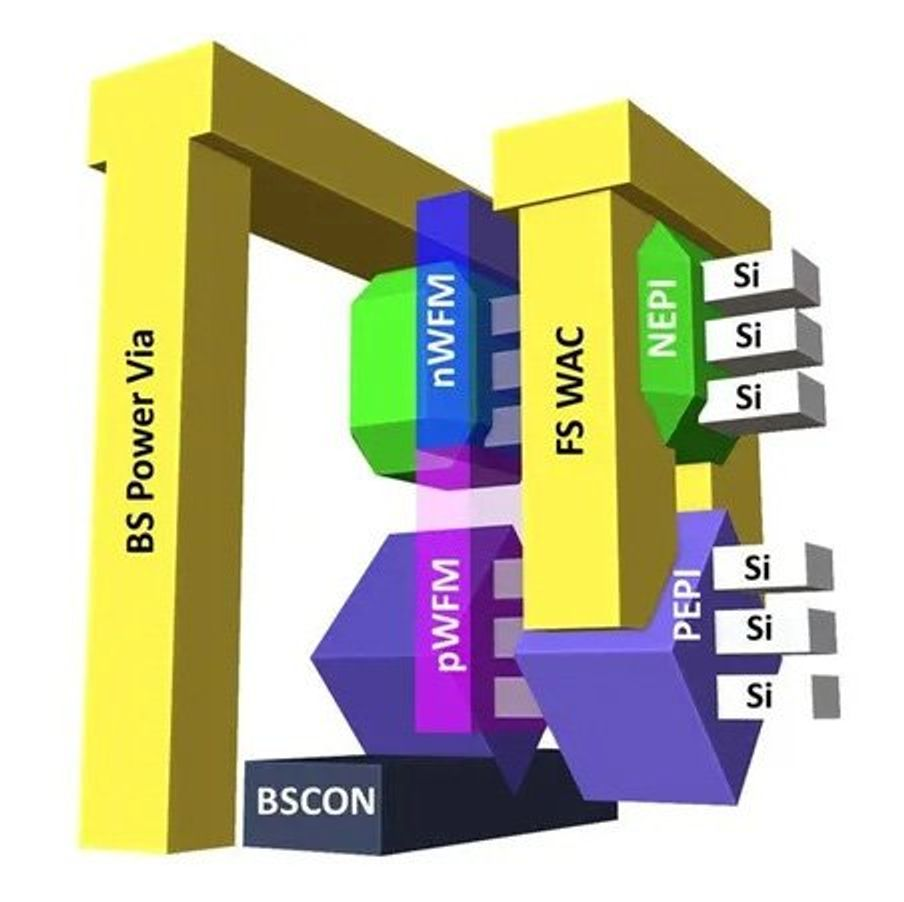

英特尔的逆变器电路依赖于一种连接顶部和底部晶体管 [黄色] 并从硅下方接触其中一个晶体管 [灰色] 的新方法

问题是,将两个晶体管堆叠成逆变器电路所需的所有互连都挤进去,会削弱面积优势。为了保持紧凑,英特尔试图消除连接到堆叠设备所涉及的一些拥塞。在当今的晶体管中,所有连接都来自设备本身之上。但今年,英特尔正在部署一种名为背面供电的技术,该技术允许在硅表面上方和下方存在互连。使用该技术从下面而不是从上面接触底部晶体管,大大简化了电路。由此产生的逆变器具有 60 纳米的密度质量,称为接触多晶间距(CPP,本质上是从一个晶体管栅极到下一个晶体管栅极的最小距离)。如今的 5 nm 节点芯片的 CPP 约为 50 nm。此外,英特尔通过将每个器件的纳米片数量从两个增加到三个,将两个器件之间的间隔从50 nm减小到30 nm,并使用改进的几何形状来连接器件的各个部分,从而改善了CFET堆栈的电气特性。

三星的秘密武器

三星甚至比英特尔更小,显示了 48 纳米和 45 纳米接触式多晶硅间距 (CPP) 的结果,相比之下,英特尔的60纳米,虽然这些都是针对个别设备,而不是完整的逆变器。虽然三星的两个原型CFET中较小的一个性能有所下降,但影响不大,该公司的研究人员相信制造工艺优化会解决这个问题。三星成功的关键是将pFET和nFET堆叠器件的源极和漏极电隔离的能力。如果没有足够的隔离,三星称之为3D堆叠FET(3DSFET)的器件将泄漏电流。实现这种隔离的关键步骤是将涉及湿化学品的蚀刻步骤换成一种新的干蚀刻。这导致优良器件的良率提高了80%。与英特尔一样,三星从硅下方接触设备底部以节省空间。然而,这家韩国芯片制造商与美国芯片制造商的不同之处在于,这家韩国芯片制造商在每个配对设备中都使用了单个纳米片,而不是英特尔的三个纳米片。研究人员表示,增加纳米片的数量将提高 CFET 的性能。

台积电出手

在本周的 IEEE 国际电子器件会议上,台积电透露了他们对 CFET 的看法——CMOS 芯片所需的逻辑堆栈与三星一样,台积电也成功实现了 48 纳米的工业相关间距。其器件的独特之处包括采用一种新方法在顶部和底部器件之间形成介电层以保持它们的隔离。纳米片通常由硅和硅锗的交替层形成。在工艺的适当步骤中,硅-锗特定蚀刻方法去除该材料,释放硅纳米线。对于用于将两个器件相互隔离的层,台积电使用了锗含量异常高的硅锗,因为知道它比其他 SiGe 层蚀刻得更快。这样,在释放硅纳米线之前,可以通过几个步骤构建隔离层。